www.electronics-usa.com

13

'21

Written on Modified on

Toshiba News

Cutting-edge Scale-Out Technology from Toshiba will Take Fintech and Logistics to New Level

Multi-chip architecture points way to continued increases in performance of Toshiba’s optimization computer. Potential to create a game-changing shift in complex financial transactions and robotics.

Toshiba Corporation (TOKYO: 6502), the industry leader in solutions for large-scale optimization problems, today announced a scale-out technology that minimizes hardware limitations, an evolution of its optimization computer, the Simulation Bifurcation Machine (SBM), that supports continued increases in computing speed and scale. Toshiba expects the new SBM to be a game changer for real-world problems that require large-scale, high-speed and low-latency, such as simultaneous financial transactions involving large numbers of stock, and complex control of multiple robots. The research results were published in Nature Electronics*1 on March 1.

Speed and scale are keys to success in industrial sectors as different as finance, logistics, and communications, all of which have to deal with large number and make complex decisions in the shortest time possible. Aiming to bring higher efficiencies to these and other businesses, Toshiba has addressed combinatorial optimization problems by developing high-speed, high-accuracy algorithms and corresponding practical computer solutions*2. The company recently announced a second generation of its simulated bifurcation algorithms, implemented on classical computers via a single field programmable gate array (FPGA), that surpasses quantum computers in obtaining optimal solutions for various combinatorial optimization problems at high speed*3.

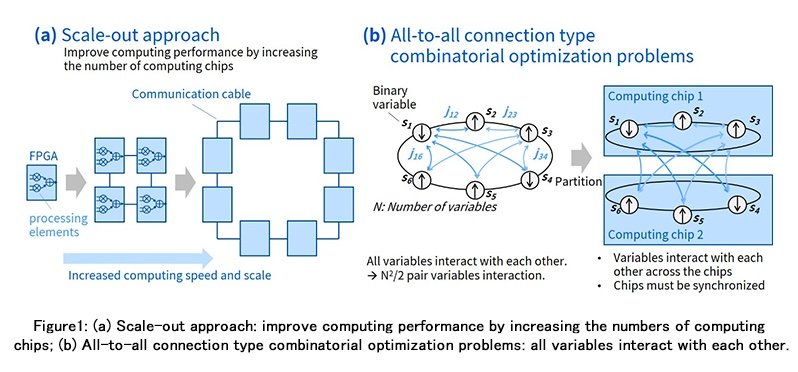

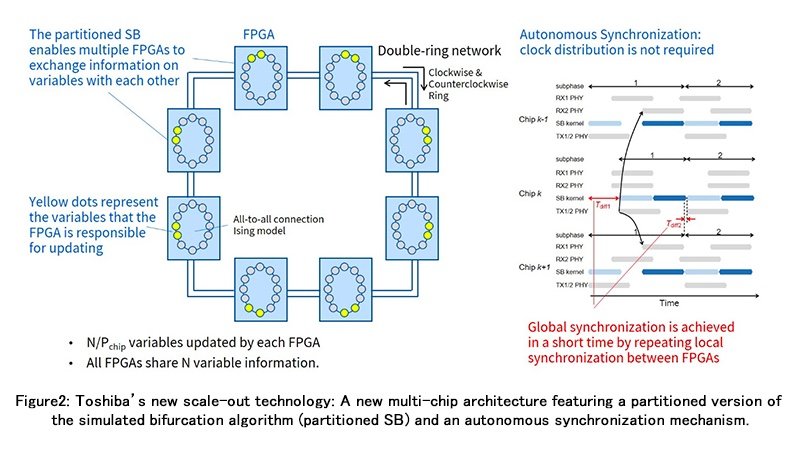

Toshiba continues to pursue better performance of the SBM by installing more FPGAs in the computer, an approach called scale-out in computer architecture, and has successfully demonstrated the world’s first*4 simultaneous scale-out of computing speed and problem size for all-to-all connection type combinatorial optimization problems*1. At the heart of the technology is a partitioned version of the simulated bifurcation algorithm that enables multiple FPGAs to exchange information on variables with each other, and that triggers an autonomous synchronization mechanism in minimizing the communications overhead to an extent that does not affect overall performance (Figures 1 & 2).

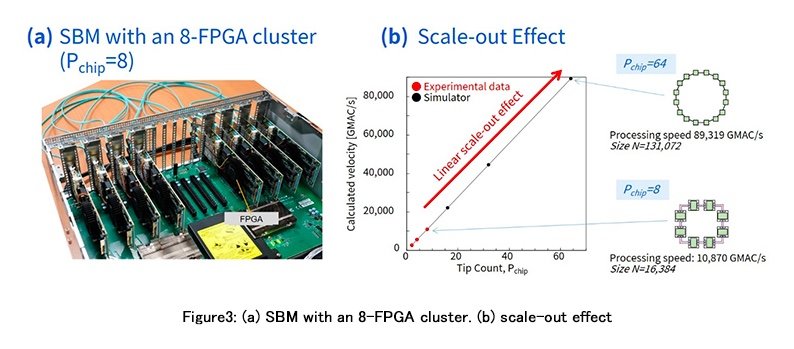

Trials has shown that an SBM with a cluster of eight FPGA (Figure 3a) achieves computational throughput 5.4 times higher than an SBM with single FPGA, and solve problems 16 times larger; and simulation results with a 64 FPGA SBM have demonstrated that the relationship between the computing speed and number of FPGA is exactly linear (Figure 3b), indicating that the technology can continue to increase the scale-out with the same effect.

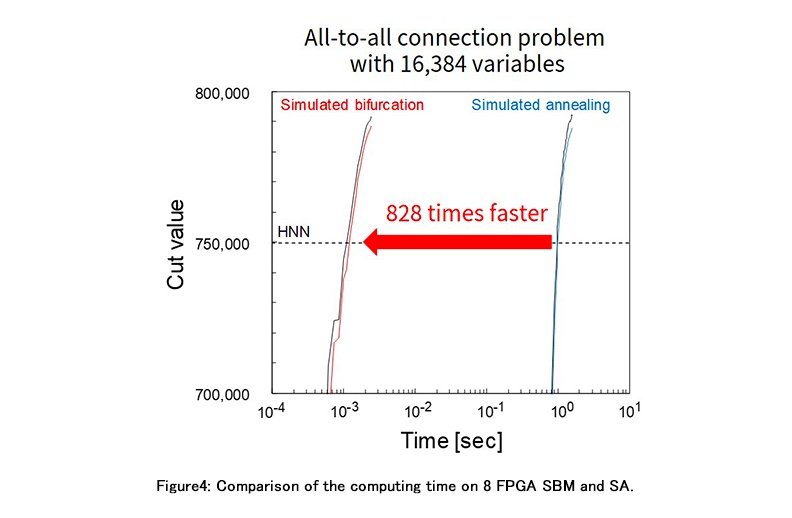

The 8 FPGA SBM also obtains solutions 828 times faster than an implementation of simulated annealing (SA), a widely used optimization technique, demonstrating that the SBM makes much more efficient use of computational resources than the SA (Figure 4).

Commenting on the application of the technology, Kosuke Tatsumura, Chief Research Scientist at Toshiba Corporation’s Corporate Research & Development Center, said: “Fast computing speed, large computing scale, and low latency to provide solutions are the critical values the new SBM can offer to business. For example, we expect the financial industry can benefit if they can trade more stocks simultaneously, and robots in the logistic industry will perform better with zero-time-lag computation. We hope the new technology will take fintech and logistic to a new level.”

*1 K. Tatsumura et al., Scaling-out Ising machine using a multi-chip architecture for simulated bifurcation, Nature Electronics 4, (2021). https://doi.org/10.1038/s41928-021-00546-4

Also see BEHIND THE PAPER: https://devicematerialscommunity.nature.com/posts/scaling-out-ising-machines

*2 H. Goto et al., Science Advances 5, eaav2372 (2019). https://advances.sciencemag.org/content/5/4/eaav2372 ; K. Tatsumura et al., IEEE Int’l Symp. on Circuits and Systems (ISCAS), 1-5 (2020). https://doi.org/10.1109/ISCAS45731.2020.9181114 ; K. Tatsumura et al., IEEE Int'l Conf. on Field-Programmable Logic and Applications (FPL), 59-66 (2019). https://doi.org/10.1109/FPL.2019.00019

*3 Toshiba’s New Algorithms Quickly Deliver Highly Accurate Solutions to Complex Problems & H. Goto et al., Science Advances 7, eabe7953 (2021). https://advances.sciencemag.org/content/7/6/eabe7953

*4 Toshiba survey.

www.toshiba.com